華為近日向大陸國家知識產權局提交一項名為「四晶片封裝」(quad‑chiplet)專利,該專利不僅引起兩岸業界和媒體關注,還被認為是在半導體封裝領域的一次重大突破。這項技術有望應用於華為下一代AI加速器Ascend(昇騰)910D,並可能顛覆目前由台積電主導的先進封裝市場。對華為而言,這不僅是技術挑戰,更是全球市場競爭的另一大步。

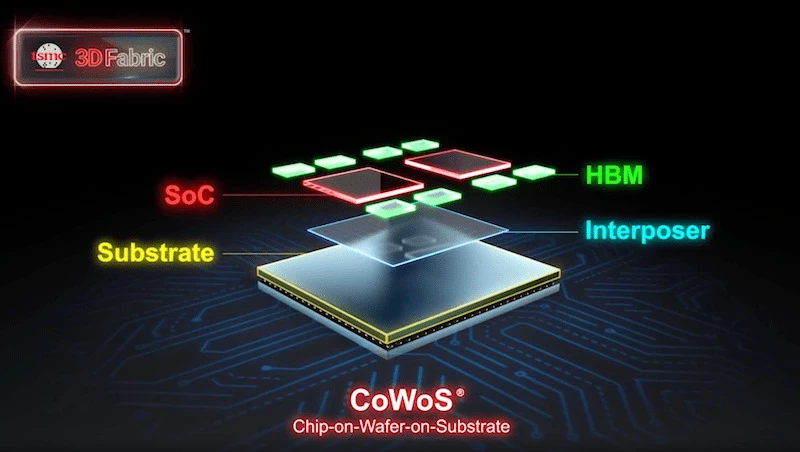

根據《Tom’s Hardware》報導,華為的四晶片封裝專利採用「橋接式」連接設計,這一設計與台積電的CoWoS-L和英特爾的EMIB/Foveros 3D封裝技術高度相似。該技術結合多組高帶寬記憶體(HBM),能實現高密度AI算力整合。與傳統單一晶片封裝相比,這種多晶片集成的封裝技術,將有效彌補華為製程技術的劣勢,並進一步提升AI運算效率和性能。

尺寸規模:等同五張EUV光罩

專利文件顯示,華為計劃將Ascend 910D加速器設計分為4片面積約665mm²的晶粒,並搭配1,360mm²的HBM記憶體,總矽面積將達2,660mm²,整體封裝面積達到約4,020mm²。這個尺寸相當於台積電目前使用的EUV晶圓光罩的五倍,顯示出華為在封裝技術上的野心和挑戰難度。如果這項技術能成功實現量產,將成為中國半導體封裝技術的重大突破。

大陸半導體分析師曹博表示:「封裝技術對中國半導體產業來說是個突破口,即使我們的製程技術存在差距,通過晶片的組合和集成,依然可實現接近甚至超越的性能。」他認為,這項四晶片封裝技術將成為華為與國際競爭對手抗衡的重要工具。

但台灣封裝技術專家張瑞華提醒,「台積電在CoWoS、InFO-WLP等先進封裝技術上處於全球領先地位。華為若想超越台積電,除了要在技術上保持突破,還需在良率和量產穩定性方面有所突破。」張瑞華的觀點,強調了華為在這一領域的競爭挑戰。

高層聲音:任正非與黃仁勳共同唱和

華為創辦人任正非曾多次強調,封裝技術的發展,將成為華為突破製程瓶頸的關鍵。他說,透過多晶片集群和疊加策略,華為可有效彌補現有製程技術的不足,並在競爭中爭取優勢。

另方面,Nvidia執行長黃仁勳也對此策略表示支持,認為中國擁有充足的能源與運算資源,將有助華為發展。他進一步指出,雖然中國在一些技術領域仍落後,但在封裝技術上的創新能有效抵消製程差距。

封裝成突破關鍵、直指台積電

華為目前正積極開發下一代AI加速器Ascend 920,計劃將其與Nvidia的H20系列進行競爭。《華爾街日報》說,華為計劃近期測試Ascend 910D,並預計在年內出貨910B和910C型號,預計將向國內大客戶如「字節跳動」供應逾80萬顆AI加速器。

封裝技術將是華為突圍的關鍵所在,這將對台積電在全球封裝市場的霸主地位構成直接挑戰。能否實現量產、達到預期性能和良率,將成為華為能否在AI晶片領域突破重圍的關鍵。

雖然華為「四晶片封裝」技術尚未成品化,仍需進一步驗證其實際性能和量產能力,但這舉措無疑也展示了華為在美國技術封鎖下,如何透過封裝創新來保持在全球AI晶片技術競爭中的強勁實力。